English version of this page

Next:Rückschreibestufe

Up:Strukturelle und funktionale Beschreibung

Previous:Ausführungsstufe

Inhalt

Stapelspeicher

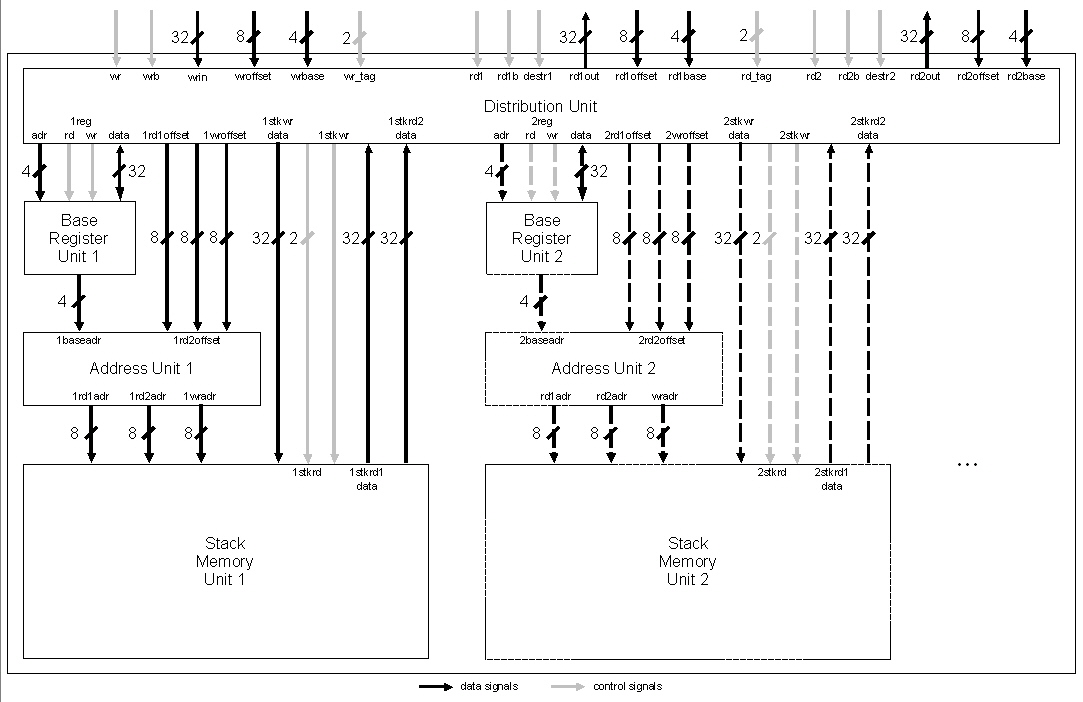

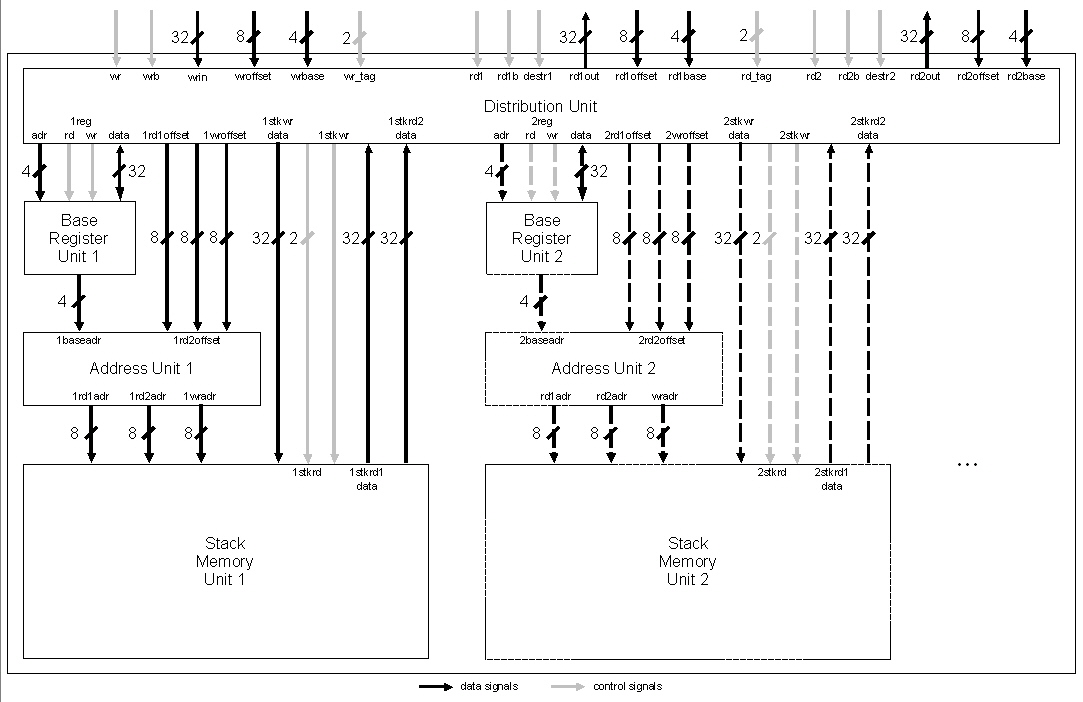

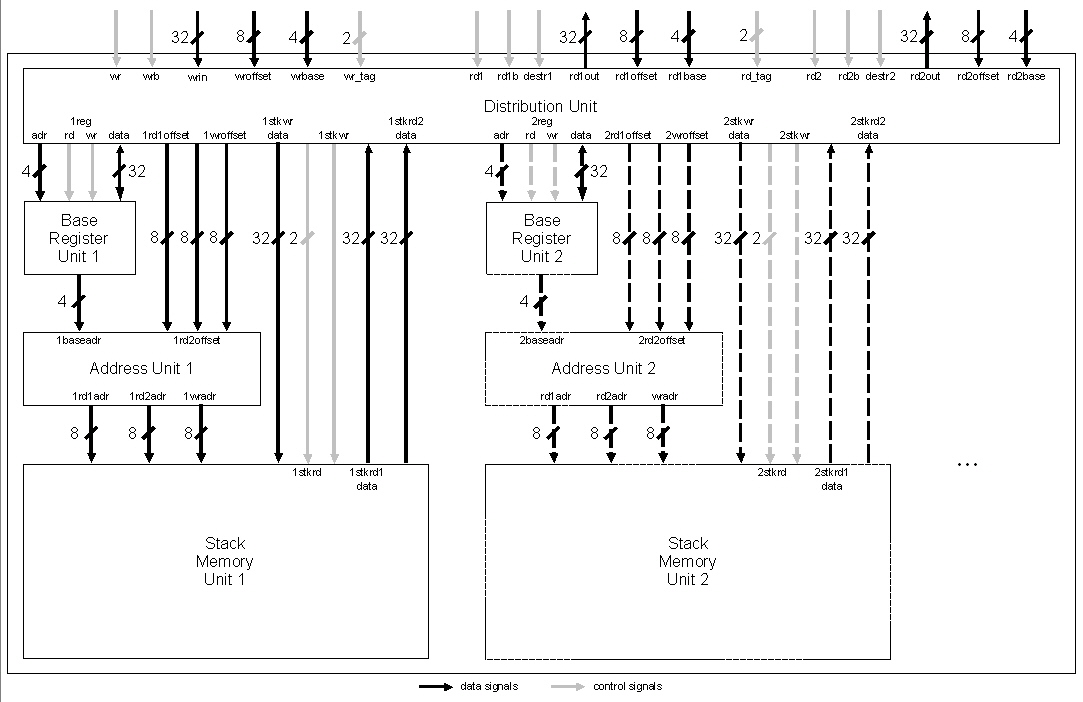

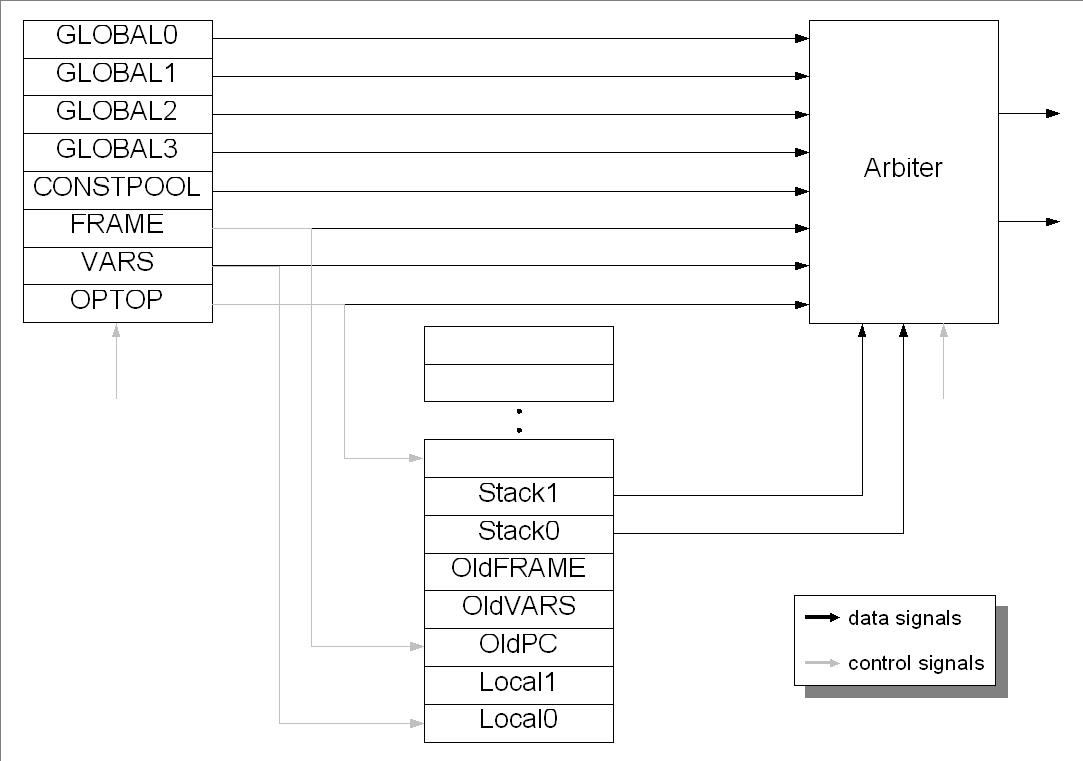

Abb. 4.11 zeigt die Stack Memory Unit (SMU),

in der sowohl der Stapelspeicher als auch die globalen Register des Mikrocontrollers

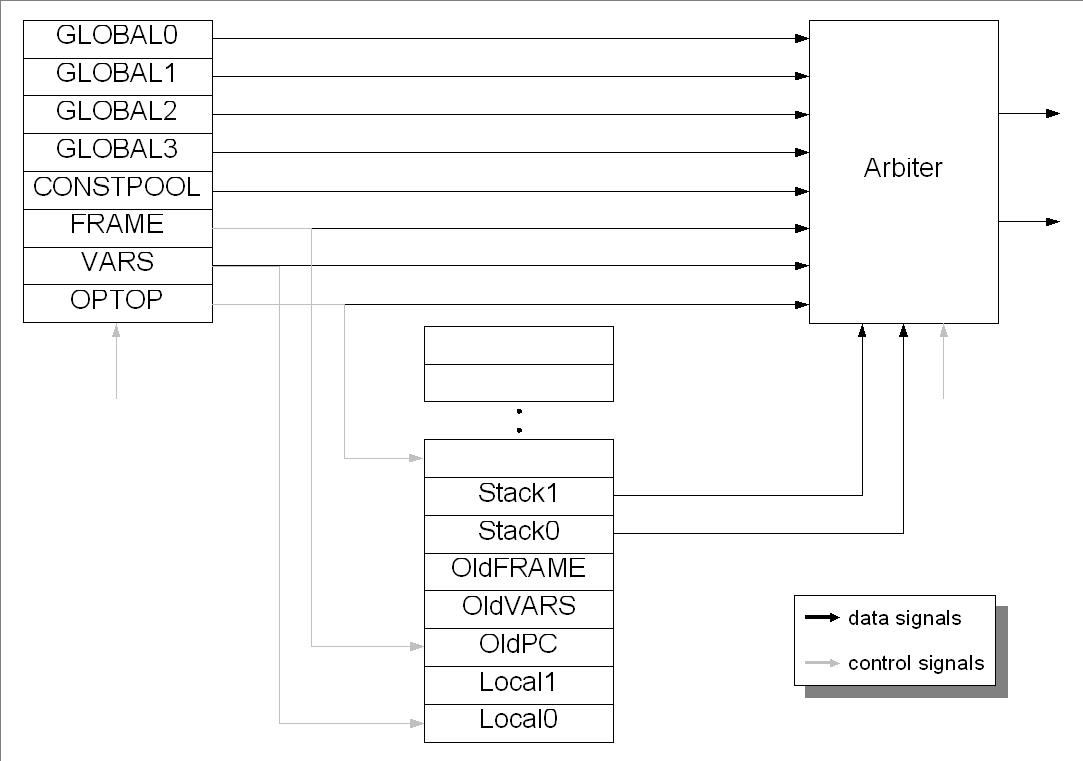

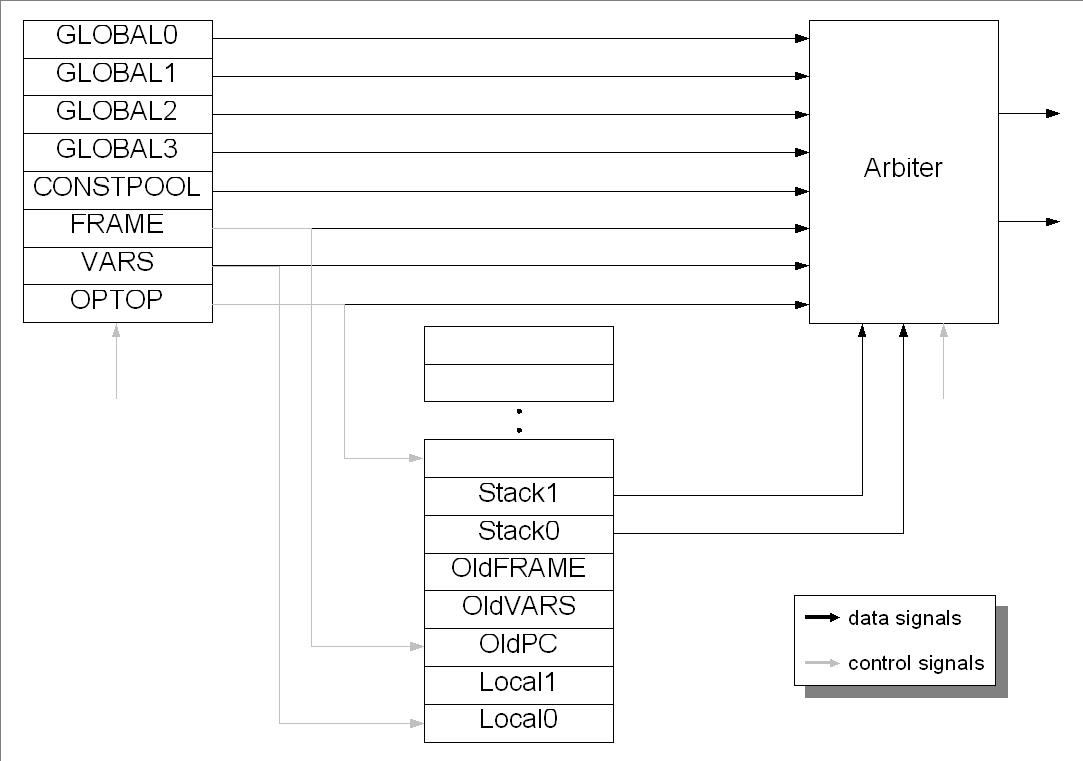

liegen. Durch Anlegen einer Basisadresse (zur Auswahl der Art des Speicher-/Registerzugriffs)

und eines Offset (Differenz) zur Auswahl der Zelle im Speicherblock wird

festgelegt, ob es sich bei dem Zugriff um eine Operation auf dem Stack

bzw. im Stack (bei instruction folding) oder etwa auf die

Basisregister handelt (vgl. Abb. 4.12).

Eine solche Aktion auf Basisregister wird der Stapelspeichereinheit durch

ein zusätzliches Signal bekanntgemacht. Wird dieses Signal nicht erkannt,

wird die Adresse für den Speicherzugriff durch Addition aus Basisadresse

und Offset ermittelt und das Datum gelesen oder geschrieben.

Abbildung 4.11: Stapelspeicherblock

Abbildung 4.12: Zugriff auf den Stapelspeicher

Damit die erforderlichen Operanden schnell verfügbar sind und auch

das am Ende der Bearbeitung einer Instruktion stehende Datum sofort in

den Stack geschrieben werden kann, ist die Stapelspeichereinheit mit zwei

Ausgängen für gleichzeitiges Lesen sowie einem Eingang für

simultanes Schreiben ausgerüstet.

Im Prototypen steht für die Realisierung des Stack nur ein Dual-Ported-RAM-Modul

zur Verfügung, welches im Vergleich zur restlichen Pipeline übertaktet

wird. Auf diese Weise kann mit einem Lesetakt (für maximal zwei Daten)

und einem Schreibtakt (für maximal ein Datum) die gewünschte

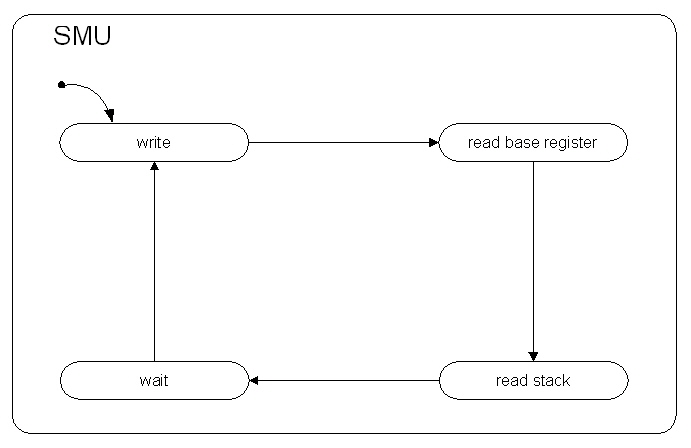

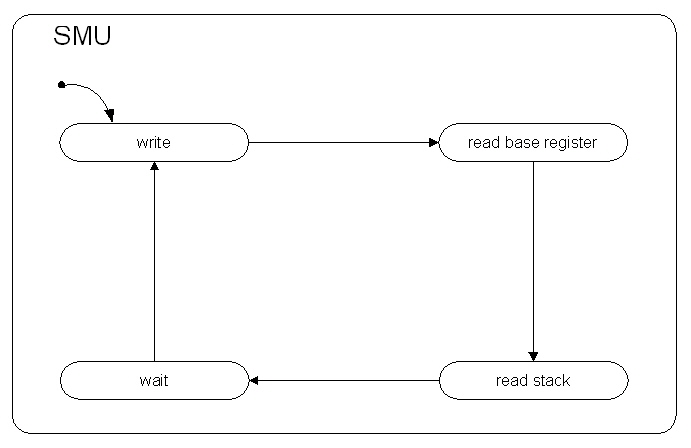

Funktionalität nachgebildet werden, wie aus dem Statechart (Abb. 4.18)

zu ersehen ist.

Abbildung 4.18: Zustandsdiagramm der Stapelspeichereinheit

Next:Rückschreibestufe

Up:Strukturelle und funktionale Beschreibung

Previous:Ausführungsstufe

Inhalt

Robert Zulauf

2000-04-27