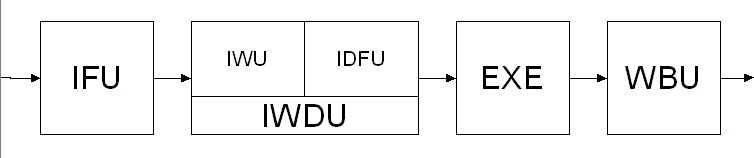

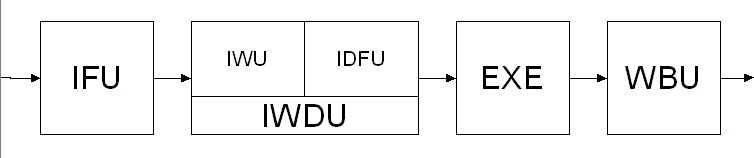

Abbildung 4.2: Pipeline of the Java-microcontroller

The memory model defines organization of address and data busses. That is why it effects the microprocessor's internal structure.

Interaction between memory, registers and instructions shows the different possibilities of accessing operands.

The model of programming contains directly accessable registers, machine instructions as well as possible ways of addressing operand registers.

Those fundamental specifications are partly defined by the objective of direct execution of Java-Bytecode in hardware, others ensue from the size of this programmable logic device. All in all the following constraints are to be met:

External bus width is 32 Bit. This follows the data structure of Java-Bytecode for data busses and shall be used for address busses, too. The instruction set is defined for a stack architecture, addressing modes of operand registers are therefore restricted. Formal Characteristics of a load/store architecture will be implemented, so that external memory access is only possible via load/store instructions. Those instructions will also use the stack. Additionally, later support of instruction folding like implemented in picoJava-II(TM) means slight modifications of the stack structure: For example data in the stack shall be accessed directly. Implementation of instruction folding is no objective of this present work but is made easier by the design explain here. Pipeline stages are given by specification of the Komodo-Mikrocontroller and can be seen in fig. 4.2): instruction fetch, instruction decode, execution with memory access and write back. Descriptions of all functional units can be found in section 4.4.

Base register which can be directly accessed by the user are:

Completely accessable by the programmer though no base registers are all entries in stack.

There are some extra registers located in the execution unit, the program counter is a register in the instruction fetch unit. All other registers are located in the stack memory unit (see section 4.4.5). This means they can be accessed like entries on the stack. Again there has to be a compromise between number of entries and used space in the chip. In this prototype the SMU holds 8 base registers and a stack memory that contains of 16 entries. All stack entries are 32 Bit wide, as well as the global registers and CONSTPOOL. This means a flexibility in programming - one program needs a bigger stack, the other one more local variables. Of course such a small number of stack entries limits use of the pipeline, but remember: This is a prototype. With a device carrying greater gate equivalent count than the XC 4036 XL a bigger stack could be implemented indicating less restrictions. An interesting question for following activities would be whether the size of the stack memory unit can be optimized with respect to space and application.

This microcontroller is capable of the address modes:

Instructions to be implemented in this prototype of pipeline are shown in table 4.1. Address modes are defined in section 4.4.3.

The design is done unitwise. That is why analysis and expansion of the units can be done faster and with less use of memory. The blocks can easily be exchanged after revision also. Following the right turn in development of the pipeline an opportunity of easy testing in simulation and on the testboard can be reached.