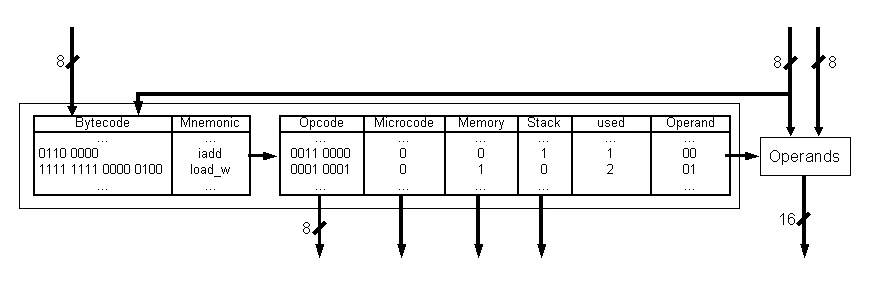

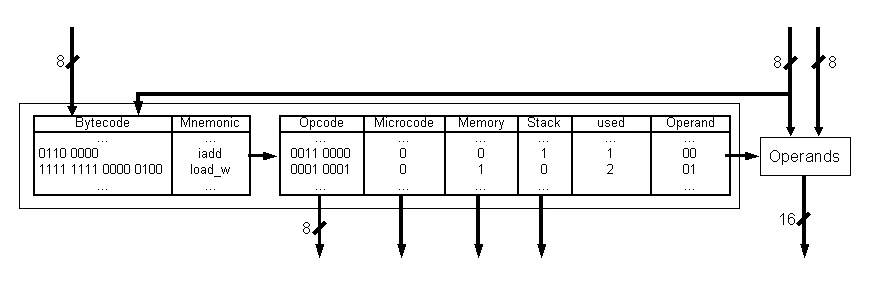

Abbildung 4.7: Umsetzung Bytecode in Steueranweisungen

Die Instruktionen gehören folgenden Funktionsgruppen an: Die Gruppe

Kontrollfluß übernimmt Steueraufgaben im Programmablauf.

Stack, Load und Store beinhalten Befehle für

den Zugriff auf Einträge im Stapelspeicher (Stack und lokale Variablen).

Mit Instruktionen aus den Gruppen arithmetisch und logisch

wird die Verarbeitung in der ALU gesteuert, die Gruppen If und

Cmp beeinflussen die Branch Control Unit, die ebenfalls in der

Ausführungsstufe angesiedelt ist. In der letzten Gruppe erweitert

sind die Instruktionen zusammengefaßt, die als erweiterte Bytecodes

Zugriffe auf die Hardware bewerkstelligen sollen. Für die Kodierung

siehe auch Abschnitt 4.5.

| BC-Mnemonik | Bytecode | Mnemonik | Opcode | Gruppe | Impl.-Art |

| aconst_null | 0x01h | push | 0100 0000 | Stack | direkt |

| iconst_m1 | 0x02h | ||||

| iconst_0 | 0x03h | ||||

| iconst_1 | 0x04h | ||||

| iconst_2 | 0x05h | ||||

| iconst_3 | 0x06h | ||||

| iconst_4 | 0x07h | ||||

| iconst_5 | 0x08h | ||||

| bipush | 0x10h | ||||

| sipush | 0x11h | ||||

| iload | 0x15h | loadv | 0001 0000 | Load | direkt |

| aload | 0x19h | ||||

| iload_0 | 0x1Ah | ||||

| iload_1 | 0x1Bh | ||||

| iload_2 | 0x1Ch | ||||

| iload_3 | 0x1Dh | ||||

| aload_0 | 0x2Ah | ||||

| aload_1 | 0x2Bh | ||||

| aload_2 | 0x2Ch | ||||

| aload_3 | 0x2Dh | ||||

| iaload | 0x2Eh | aload | 0001 1000 | Load | Mikrocode |

| istore | 0x36h | storev | 0010 0000 | Store | direkt |

| astore | 0x3Ah | ||||

| istore_0 | 0x3Bh | ||||

| istore_1 | 0x3Ch | ||||

| istore_2 | 0x3Dh | ||||

| istore_3 | 0x3Eh | ||||

| astore_0 | 0x4Bh | ||||

| astore_1 | 0x4Ch | ||||

| astore_2 | 0x4Dh | ||||

| astore_3 | 0x4Eh | ||||

| iastore | 0x4Fh | astore | 0010 1000 | Store | Mikrocode |

| dup | 0x59h | loado | 0001 0001 | Load | direkt |

| iadd | 0x60h | add | 0011 0000 | arithmetisch | direkt |

| isub | 0x64h | sub | 0011 0001 | arithmetisch | direkt |

| imul | 0x68h | mul | 0011 0100 | arithmetisch | direkt |

| idiv | 0x6Ch | div | 0011 0101 | arithmetisch | direkt |

| ineg | 0x74h | neg | 1100 0000 | logisch | direkt |

| ishl | 0x78h | shl | 1100 0001 | logisch | direkt |

| ishr | 0x7Ah | shr | 0011 0010 | arithmetisch | direkt |

| iand | 0x7Eh | and | 1100 0011 | logisch | direkt |

| ior | 0x80h | or | 1100 0100 | logisch | direkt |

| ixor | 0x82h | xor | 1100 0101 | logisch | direkt |

| iinc | 0x84h | iinc | 0011 0010 | arithmetisch | direkt |

| ifeq | 0x99h | ifeq | 0101 0000 | If | direkt |

| iflt | 0x9Bh | iflt | 0101 1001 | If | direkt |

| if_icmpeq | 0x9Fh | braeq | 1010 0000 | Cmp | direkt |

| if_icmplt | 0xA1h | bralt | 1010 1001 | Cmp | direkt |

| load_word | 0xFFx04h | load_w | 0001 0001 | Load | direkt |

| store_word | 0xFFx24h | store_w | 0010 0001 | Store | direkt |

| read_pc | 0xFFx40h | r_pc | 1111 0000 | erweitert | direkt |

| read_optop | 0xFFx43h | r_optop | 1111 0001 | erweitert | direkt |

Die Adressierungsarten sind bei einer Stack-Architektur stark eingeschränkt (wie auch in Abschnitt 4.3 diskutiert). So gibt es die indirekte Adressierung tatsächlich nur bei den Speicherzugriffen: im Prototypen existieren nur die Instruktionen load_w und store_w, bei denen diese zweite Adressierungsart auftritt, alle anderen Befehle arbeiten nur auf dem Stack und somit mit impliziter Adressierung.

Zusätzlich zur Dekodierfunktion übernimmt diese Stufe Teilaufgaben einer Operandenholestufe (OF: Operand Fetch unit). Sie legt dafür die benötigten Adressen und Signale an die Stack Management Unit (siehe Abschnitt 4.4.5) an, damit die von dort zu lesenden Operanden beim nächsten Takt in die Ausführungseinheit übernommen werden können.

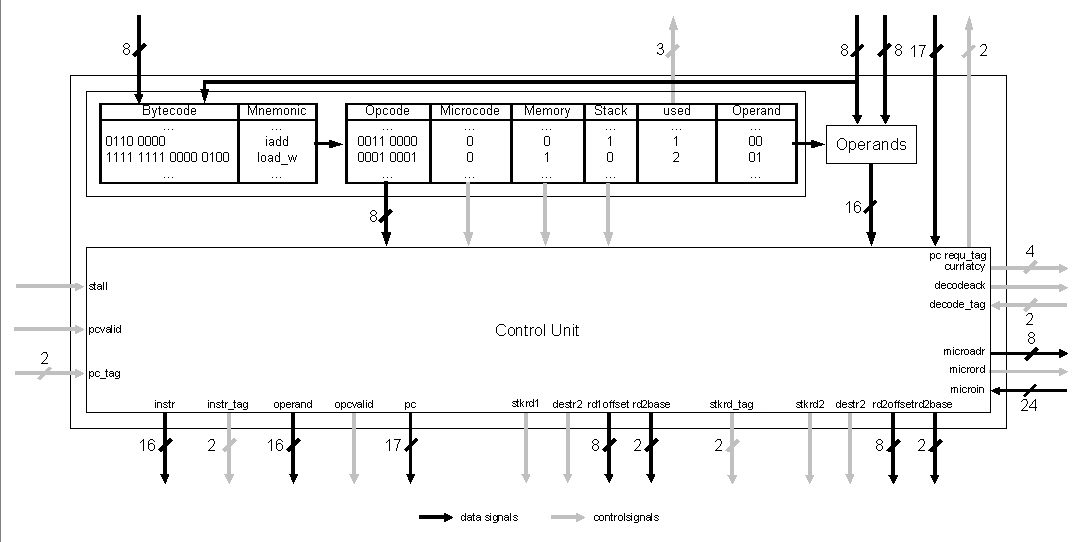

In einem späteren Stadium des Entwurfs bzw. des Projekts kann die Dekodierstufe die zusätzliche Aufgabe bekommen, eine Erkennung von data forwarding, also dem Wiederverwenden des Ergebnisses der Berechnung des letzten Taktes, durchzuführen und dies der nachfolgenden Ausführungseinheit mitzuteilen. Die gesamte Dekodiereinheit zeigt Abb. 4.8.

Der Mikroprogramm-Sequenzer (MRU: Microcode-ROM Unit) gibt nach Anforderung durch die Dekodierstufe die unter der angelegten Adresse gespeicherten Befehle Takt für Takt an die Dekodierstufe zurück. Dies geschieht mittels eines Zustandsautomaten, der im wartenden Zustand (kein Mikrocode aktiv) ständig 0xFFFFFFh ausgibt. Dieses Signal zeigt der Dekodierstufe an, daß momentan kein Befehl einer Mikrocode-Implementierung mehr folgt und somit die normale Dekodierung mit anschließender Freigabe für die Bearbeitung durch die Ausführungsstufe erfolgen kann.

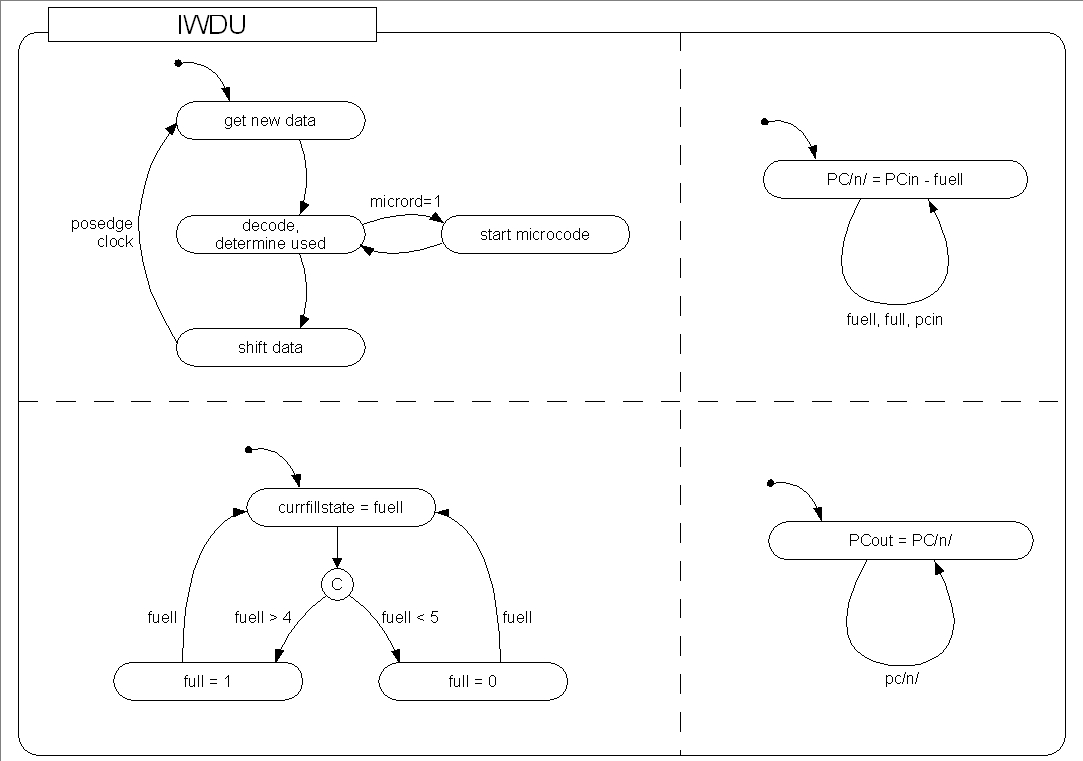

Die vier nebenläufigen Prozesse, die im Statechart in Abb. 4.16 zu sehen sind, stellen diese Funktionalität zur Verfügung: In einem Prozeß wird die Bearbeitung der Befehlsdaten vorgenommen (puffern, dekodieren, schieben), in den anderen Prozessen werden Daten wie Füll- oder Befehlszählerstände berechnet und ausgegeben.

Abbildung 4.16: Zustandsdiagramm der Befehlspuffer- und Dekodierstufe